### SWIFT<sup>®</sup> PACKAGING CONSIDERATIONS

Amkor's state-of-the-art High-Density Fan-Out (HDFO) structure called Silicon Wafer Integrated Fan-out Technology (SWIFT) packaging, bridges the gap between TSV and laminate substrates.

#### FEATURES

- Polymer dielectrics

- Multi-die and large die capability

- Large body package capability

- Interconnect density down to 2/2 µm

- Cu pillar die interconnect down to 30 µm pitch

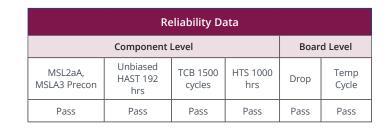

- Meets JEDEC MSL2a and MSL3 CLR and BLR requirements

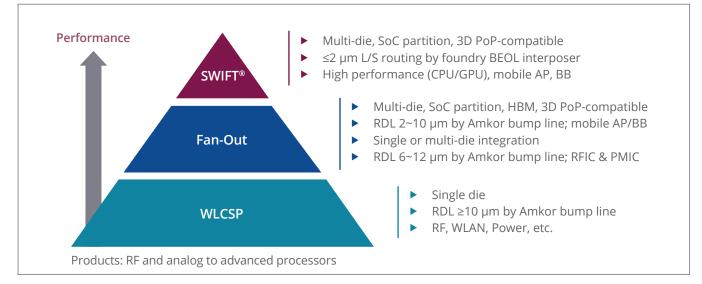

### **TECHNOLOGY SOLUTIONS**

# SWIFT<sup>®</sup> Technology

Silicon Wafer Integrated Fan-out Technology (SWIFT) is designed to provide increased I/O and circuit density in a reduced footprint and profile for single and multi-die applications. SWIFT technology enables creation of advanced 3D structures, addressing the need for increased IC integration in emerging mobile and networking applications.

The distinctive characteristics of SWIFT technology are due, in part, to the fine feature capabilities associated with this innovative wafer level packaging technique. This allows more aggressive design rules to be applied compared to traditional WLFO and laminate-based assemblies.

### SWIFT Structures and Attributes

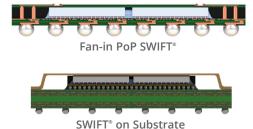

The figure below shows cross-section illustrations of a single die SWIFT and dual-die 3D/Package-on-Package (PoP) SWIFT structures. Although the package appears to be of a typical fine-pitch flip chip construction, it incorporates some unique features not

associated with conventional IC packages.

## Enabling Technologies for SWIFT Packaging

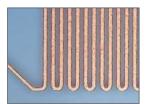

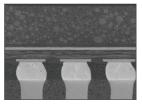

Key assembly technologies enable the creation of these distinctive SWIFT packaging features and attributes. Through the use of stepper photo imaging equipment, 2/2 µm line/space features can be achieved, enabling very high density die-to-die connections required for SoC partitioning and networking applications where 2.5D TSV would typically be used. Fine-pitch die micro bumps provide a high-density interconnect for advanced products, such as application processors and baseband devices. In addition, tall Cu pillars enable a high-density vertical interface for mounting advanced memory devices on the top of the SWIFT structure.

Plated Cu RDL L/S down to 2 µm

Multilayer Redistribution

Multilayer RDL Cross Section

Tall Cu Pillar for PoP Applications

# SWIFT<sup>®</sup> Technology

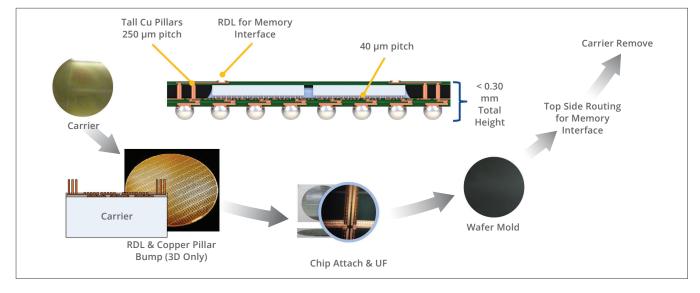

### SWIFT Packaging Process Flow

SWIFT product attributes are realized by applying a unique process flow that incorporates both flip chip assembly and wafer level processing techniques, as shown below.

### SWIFT Packaging Technology Process Flow

### Advanced Wafer Product Positioning

### Visit amkor.com or email sales@amkor.com for more information.

With respect to the information in this document, Amkor makes no guarantee or warranty of its accuracy or that the use of such information will not infringe upon the intellectual rights of third parties. Amkor shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon it and no patent or other license is implied hereby. This document does not in any way extend or modify Amkor's warranty on any product beyond that set forth in its standard terms and conditions of sale. Amkor reserves the right to make changes in its product and specifications at any time and without notice. The Amkor name and logo are registered trademarks of Amkor Technology, Inc. All other trademarks mentioned are property of their respective companies. © 2018 Amkor Technology Incorporated. All Rights Reserved. TS110D Rev Date: 9/18